## 基于 FPGAOL 的 CPU 调测试系统设计及应用\*

#### 樊彦恩 张俊霞 卢建良 赵雅楠 吴骏东

中国科学技术大学计算机科学与技术学院, 合肥 230028

**摘 要** 在计算机组成原理的实验课程教学中,处理器设计实验能够使学生深入理解和掌握计算机的运行和控制机制。为了保证处理器设计的正确性,需要进行一系列测试和调试,因此需要一个处理器调测试系统。本文设计实现了一种基于 FPGA 在线实验平台(FPGA Online: FPGAOL)的 CPU 调测试系统。学生根据 RISC-V 指令集自由设计完成 32 位 CPU 的数据通路和控制器,就可以通过调测试系统观察运行过程和结果以确定 CPU 设计的正确性。

关键字 计算机组成原理,处理器,调测试系统,FPGAOL,RISC-V

# Design and Application of CPU Debug and Test System Based on FPGAOL

Fan Yanen Zhang Junxia Lu Jianliang Zhao Yanan Wu Jundong

School of Computer Science and Technology,

University of Science Technology of China,

Hefei 230026, China;

fye1985@ustc.edu.cn

Abstract— In the course of computer composition, the design of CPU (Central Processing Unit) experiment can help students understand and master the control and operating mechanism of computer. In order to validate the design of CPU, a system that can accomplish a serial of testing and debugging is required. In this paper, a CPU debug and test system based on FPGAOL (FPGA Online) is proposed. Students can design the data path and controller of 32-bit CPU freely according to the RISC-V instruction set. After that, they can analyze the data produced during process of CPU running to determine the correctness of the CPU design.

Keywords—Computer Composition Principle, CPU, debug and test system, FPGAOL, RISC-V

## 1 引言

随着"计算机组成原理"课程教学改革的进行,基于 FPGA 的 CPU 设计已成为这门课程实验的重要组成部分[1]。根据教育部十二五规划对教育信息化的要求,中国科学技术大学计算机实验教学中心组织开发了线上硬件实验平台 FPGAOL (FPGA Online),该实验平台将 FPGA 部署在云上,实现了实验资源的高效利用,也能帮助有需要的师生随时随地访问 FPGA 资源。

在计算机组成原理实验课程中加入 CPU 设计可以帮助学生理解计算机的组成结构和工作原理[2]。同时,该门课程配套理论教材已经给出基于运算、访存和转移三类指令的数据通路以及控制器设计的关键原理。从学生做实验的周期来看,设计所占的比重其实是很小的,比较耗时的是仿真和调试[3]。学生可以通过仿真工具对自己的设计进行验证,但经常会碰到仿真上板行为不一致,更多时候是仿真正常,上板异常。由于 CPU 数据通路比较复杂,一旦出现问题,如果缺乏

\*基金资助:本文得到中国科学技术大学 2022 年度校级质量工程教学研究重点项目(2022xjyxm008)资助。

有效的调试工具,很难定位错误。清华大学的计算机组成原理实验采用 TEC-CA-I 开放式 CPU 教学实验系统,该系统由 PC 监控系统、控制电路和 FPGA-CPU 组成,使用时将设计的 CPU 下载到 FPGA 上,通过 PC 监控系统下载运行程序进行调试 [4-6]。西安石油大学也有报道研制基于 FPGA 的开放式 CPU 实验平台 [7-8]。通过该实验平台,学生可以根据自行选取的 MIPS 指令集修改模型机的数据通路和控制通路并设计控制器,通过实验平台观察运行过程和结果以确定设计的正确性。

本文旨在 FPGAOL 实验平台上,为学生自主设计的基于 RISC-V 指令架构的 CPU 提供调测试系统,从而完成 CPU 的功能验证和测试。学生根据选定的 RISC-V 指令采用 verilog 语言构建完整的 CPU 数据通路,并设计相应的控制器。在设计 CPU 功能部件时,增加用于调试的接口。然后将 CPU 模型机模块移植到调测试系统的 vivado 工程中,生成 bit 文件,通过 FPGAOL 实验平台下载至远程 FPGA 芯片中。最后利用 FPGAOL 实验平台的串口调试工具,输入自定义指令,控制 CPU 模型机工作在连续或单步运行状态,从而实现 CPU 的

Journal of Computer Technology and Education

功能测试和调试。另外, CPU 调测试系统提供 RV32I 指令自动化测试的汇编程序以及目标代码,利用 XILINX FPGA 中指令存储器 RAM IP 的初始内容加载功能,将目标代码装载到 RAM 中,供 CPU 执行。

#### 2 FPGAOL 实验平台简介

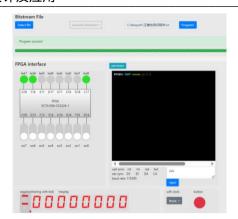

FPGAOL 实验平台操作界面如图 1 所示,主要包括代码烧写区、拨码开关输入区、数码管显示区和串口调试区。用户将 vivado 工程生成的 bit 文件通过界面烧写到后台的 FPGA 芯片。若程序中使用了 FPGAOL 实验平台中的外设:拨码开关和数码管,就可以在界面上通过拨码开关输入数据,同时也可以将输出数据显示在数码管上。除此之外,FPGAOL 实验平台界面提供了串口调试工具。本文中介绍的 CPU 调测试系统就是通过 FPGAOL 实验平台的串口调试工具实现的。

图 1 FPGAOL 实验平台界面

## 3 CPU 调测试系统设计

#### 3. 1 CPU 调测试模型架构及工作模式

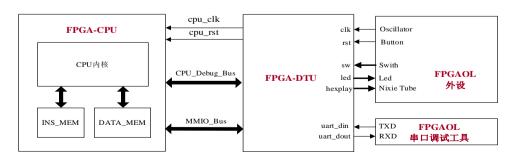

整个 CPU 调测试系统分为四大部分,即模型机 FPGA-CPU、调测试控制模块 FPGA-DTU、FPGAOL 平台外

围设备和串口调试工具。其中 FPGA-DTU 是 CPU 调测试系统的核心,如图 2 所示。它负责与串口调试工具通信,接收串口调试工具发送过来的指令,然后将模型机 FPGA-CPU 中的调试数据显示在数码管上;控制FPGA-CPU 的运行状态;管理 FPGAOL 外设,控制外设和 CPU(或内存)之间交换数据。FPGA-CPU 和 FPGA-DTU均采用 verilog 硬件描述语言设计,最后在 FPGAOL 平台的远程 FPGA 芯片上实现。

FPGAOL 平台外围设备中的 Led 灯用于指示调测试系统的工作状态,如表 1 所示。Led [7]为 CPU 运行状态指示灯。当 Led [7]亮起时,指示 CPU 正在运行;当 Led [7]熄灭时,指示 CPU 停止运行,处于调试状态 (单步运行);系统上电初始状态为 CPU 调试状态。Led [6:4]指示数码管显示数据的不同含义:Led [6]指示 CPU 运行过程中,与外设交互时,开关实时输入的数据;Led [5]指示 CPU 运行过程中,与外设交互时,CPU 输出的数据;Led [4]指示 CPU 处于调试状态时,数码管显示 CPU 数据通路中的数据。Led [3]指示在 CPU 运行过程中,与外设交互时,CPU 等待开关输入数据;Led [2]指示在 CPU 运行过程中,与外设交互时,CPU 等待用户查看数码管显示数据。CPU 调测试系统提供 RV32I 指令的汇编测试程序,Led [1]和 Led [0]用于指示 CPU 运行汇编测试程序的结果。

表 1 调测试系统工作状态指示

| 指示灯状态  | 1 (亮)          | 0 (灭)       |

|--------|----------------|-------------|

| Led[7] | CPU运行状态        | CPU调试<br>状态 |

| Led[6] | 数码管显示开关输入数据    | -           |

| Led[5] | 数码管显示CPU运行输出数据 | -           |

| Led[4] | 数码管显示CPU调试数据   | -           |

| Led[3] | CPU等待开关数据输入    | -           |

| Led[2] | CPU等待数码管数据读取   | ı           |

| Led[1] | CPU运行指令失败      |             |

| Led[0] | CPU运行指令成功      | -           |

图 2 基于 FPGAOL 的 CPU 调测试系统原理图

#### 3. 2 模型机 FPGA-CPU 设计

调测试控制模块 FPGA-DTU 通过读取模型机 FPGA-CPU 运行过程中数据通路中的数据,实现对 CPU

的功能测试和调试。被 FPGA-DTU 读取的数据分为两大类,一类是 CPU 功能部件,如寄存器堆、存储器内部数据;另一类是单周期数据通路中组合逻辑元件输出数据或流水线 CPU 段间寄存器中的数据。

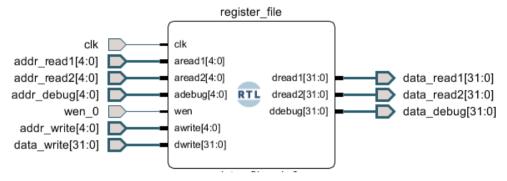

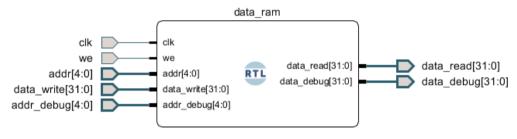

图 3 增加调试端口的寄存器堆模块

图 4 增加调试端口的数据存储器模块

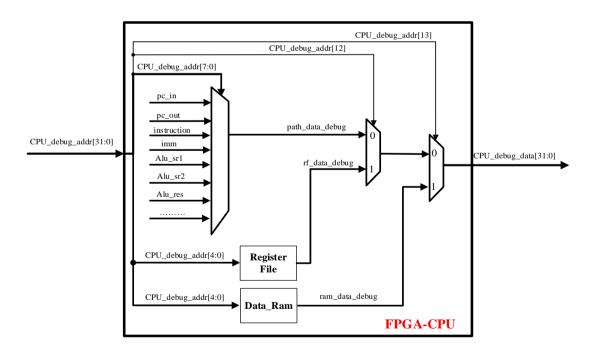

图 5 FPGA-CPU 内部调试信号逻辑关系

在设计模型机时,学生根据计算机组成原理实验课程指定的 RISC-V 指令采用 verilog 硬件描述语言设计完整的 CPU 数据通路和相应的控制器。调测试控制模块在读取模型机功能部件内部数据时,需

要尽可能不对模型机内部设计产生影响,并且不影响 CPU 正常运行,因此需要对模型机功能部件进行改造,即增加用于调试的接口如图 3 所示,寄存器堆增加了一个调试读端口: 4 位地址输入端口和 32 位

数据输出端口。同理,数据存储器也需要增加一个调试读端口,如图 4 所示。

以单周期 CPU 调试接口设计为例,图 5 给出了调试数据在 CPU 内部的逻辑设计。该调试数据采用多级选择器级联方式,实现了寄存器堆、数据存储器和数据通路路径上数据的选择输出。选择器的选择信号采用了 CPU debug addr 某一位或者某几位数据。

图 6 调试控制模块 FPGA-DTU 功能拓扑图

表 2 串口命令格式及功能

| │ 命令<br>│ 分类    | 命令格式                      | 功能                                                                                                                                                                               | 备注                                         |  |  |  |  |  |

|-----------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--|--|--|--|--|

| CPU控<br>制命<br>令 | bp+[8位十六<br>进制数];         | 设置CPU<br>运行<br>点<br>点<br>行<br>至<br>断<br>点<br>手<br>重<br>数<br>点<br>点<br>点<br>点<br>系<br>行<br>系<br>。<br>。<br>。<br>。<br>。<br>。<br>。<br>。<br>。<br>。<br>。<br>。<br>。<br>。<br>。<br>。<br>。 | 8位十六进制数为断点<br>地址                           |  |  |  |  |  |

|                 | step;                     | 控制CPU<br>单步执<br>行                                                                                                                                                                | FPGA-DTU产生一个时<br>钟信号给FPGA-CPU              |  |  |  |  |  |

|                 | run;                      | 控制CPU<br>连续执<br>行                                                                                                                                                                | FPGA-DTU产生连续时钟信号,CPU运行到断点或者结束              |  |  |  |  |  |

|                 | Rst;                      | CPU 复<br>位                                                                                                                                                                       | FPGA-DTU产生一个高<br>电平脉冲,控制PC回<br>到初始值        |  |  |  |  |  |

| CPU调<br>试命<br>令 | debug0+[2位<br>十六进制<br>数]; | 查看数<br>据路径<br>数据                                                                                                                                                                 | 2 位 16 进制数为<br>CPU_debug_addr[7:0]         |  |  |  |  |  |

|                 | debug1+[2位<br>十六进制<br>数]; | 查看寄<br>存器堆<br>数据                                                                                                                                                                 | 2位十六进制数为寄存<br>器堆地址<br>CPU_debug_addr[4:0]  |  |  |  |  |  |

|                 | debug2+[2位<br>十六进制<br>数]; | 查看数<br>据存储<br>器数据                                                                                                                                                                | 2位十六进制数为数据<br>存储器地址<br>CPU_debug_addr[4:0] |  |  |  |  |  |

#### 3.3 调测试控制模块 FPGA-DTU 设计

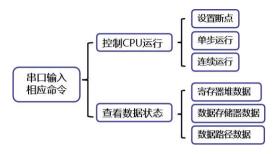

调测试控制模块 FPGA-DTU 是 CPU 调测试系统的核心,主要通过接收串口命令控制模型机 FPGA-CPU 运行方式,以及查看 CPU 内部寄存器堆、数据存储器数据以及数据路径上的数据,如图 6 所示。FPGA-CPU 的运行方式分为连续运行状态和调试状态,系统状态指示灯如表 1 所示。连续运行时,FPGA-DTU 产生连续时钟信号,CPU 运行到断点结束,同时系统会给出 CPU 运行的结果。在调试状态(单步运行)时,

FPGA-DTU产生一个时钟信号给 FPGA-CPU,此时可以通过串口命令静态获取 CPU 每一个时钟运行后的内部数据。

调测试控制模块主要通过接收串口命令运行,因此串口命令的设计非常关键。串口命令主要分为两大类: CPU 控制命令和调试命令。以单周期 CPU 为例,CPU 控制、调试命令格式及功能如表 2 所示。需要注意的是,断点地址和调试地址(CPU\_debug\_addr)应为 4 的整数倍,且一次只能设置一个断点; step指令会覆盖先前设下的断点; 在使用 run 命令之前,需要先通过断点命令(bp)设置断点。不同调试数据的输出是通过调试地址 CPU\_debug\_addr[13:12]选择输出的。

调测试控制模块 FPGA-DTU 还具有选择、分配外设, 控制外设和 FPGA-CPU 之间交换数据。CPU 采用程序查询的方式判断外设是否准备好接收数据或者准备好向 CPU 输入数据。

#### 4 CPU 调测试系统整体测试

将模型机 FPGA-CPU 模块移植到调测试系统的 vivado 工程中(该工程中已经将调测试控制模块 FPGA-DTU 和模型机的控制接口和调试接口处理好), 然后生成 bit 文件后下载至 FPGAOL 实验平台远程 FPGA 芯片中。利用 FPGAOL 实验平台的串口工具,输 入自定义串口命令控制 CPU 运行方式并查看调测试 数据。将 RV32I 指令自动化测试的目标代码预先加 载至指令存储器中,当 FPGA-CPU 数据通路设计正确 时,系统指示灯Led[0]亮起;当FPGA-CPU数据通路 设计错误时,系统指示灯 Led[1]亮起。当数据通路 设计有误时,学生就可以通过串口命令控制 CPU 工 作在调试状态,对数据通路中的关键数据进行查看。 这种自动化测试方式提高了实验检查的效率,节省 了助教和学生的时间。调测试系统初始上电默认进 入调试状态,界面如图 7 所示, Led[4]点亮,指示数 码管显示调试数据,此时默认显示的是 PC 值。在串 口输入 "run;"命令, FPGA-CPU 连续运行, Led[7] 点亮。此时待测试模型机 FPGA-CPU 数据通路设计正 确, Led[0]点亮, 如图 8 所示。

## 5 CPU 调测试系统学期测评

经过近两年对计算机组成原理实验课程中 CPU 调测试方法的不断改进和摸索,初步确定了利用 FPGAOL 实验平台中串口调试工具构建 CPU 调测试系统方案。该 CPU 调测试系统在 2023 年春季学期计算机组成原理实验课程中得到初步验证。从学生调试 CPU 的过程、课程群中实验问题情况和助教检查实验情况来看,CPU 调测试系统确实提高了学生做实验和助教检查实验的效率。

图 7 调测试系统上电初始界面

图 8 FPPGA-CPU 设计正确调测试界面状态

表 3 结课后学生的问卷调查结果

| 分数        | 5分      | 4分     | 3分     | 2分     | 1分     |

|-----------|---------|--------|--------|--------|--------|

| 自由查看数据通路  | 79. 41% | 8.82%  | 5. 88% | 5.88%  | 0      |

| 展示CPU运行结果 | 85. 29% | 5. 88% | 5. 88% | 2.94%  | 0      |

| 实现外设便捷交互  | 82. 35% | 2.94%  | 8.82%  | 2.94%  | 2.94%  |

| 使用简单易上手   | 82. 35% | 5.88%  | 5. 88% | 2.94%  | 2.94%  |

| 简化个人调试流程  | 79. 41% | 2.94%  | 8. 82% | 0      | 8. 82% |

| 提高实验检查效率  | 73. 53% | 14.71% | 5. 88% | 5. 88% | 0      |

表 3 为课程结束后,对学生发放的调查问卷,从 六个方面调查学生对 CPU 调测试系统的体验效果。 从问卷结果来看,CPU 调测试系统的基本功能得到初步验证,学生的体验效果达到了预定目标。

#### 6 結束語

课题组经过不断探索,以为本校计算机专业学生提供良好实践课程体验为目标,不断优化升级计算机组成原理实验课程的软硬件设施,同时开发多样化的调试平台,提升大学低年级学生编程兴趣,增强学生实践编程能力,为高年级综合实践类课程学习奠定了基础。学生对 CPU 调测试系统的体验效果问卷也给出了调测试系统存在的不足以及需要改进的地方,在今后的教学中,将会对 CPU 调测试系统进行更深入、细致的改进,提升学生实验体验效果。

## 参考文献

- [1] 王力生, 余智铭, 张冬冬. "计算机组成原理"实验 CPU 设计方法研究[J]. 实验技术与管理, 2018, 35(05):1-5+9.

- [2] 陈秋莲,陈芷,尹梦晓,吴旭. 计算机组成原理课程思 政混合式教学探索[J]. 计算机技术与教育学 报, 2022, 10(4): 38-41.

- [3] 汪文祥, 邢金璋. CPU 设计实战[M]. 北京: 机械工业出版社, 2021: 103-104.

- [4] 张楷. 通用 CPU 实验系统的设计与实现[D]. 清华大学, 2004.

- [5] 汤志忠,杨春武.开放式实验 CPU 设计[M].北京:清华大学出版社,2007.

- [6] 李山山, 汤志忠, 周继群. 基于 FPGA 的开放式教学 CPU 的设计与测试系统[J]. 计算机工程与应 用, 2005 (14):98-100+198.

- [7] 康磊, 杨朝辉. 基于 FPGA 的开放式 CPU 实验模型设计 [J]. 电脑知识与技术, 2017, 13(30):235-237.

- [8] 唐陈辉. 一种基于 RISC-V 架构的嵌入式 SoC 系统设计 [D]. 西安电子科技大 学, 2022. DOI: 10. 27389/d. cnki. gxadu. 2022. 000521.